NNJ TPLL V1/A

## 技術ノート

REV. H

著者 : Fabrizio Francione

©2026 Nara Network Japan

[www.naranetwork.com](http://www.naranetwork.com)

周波数計測 ( Frequency Metrology ) のための、コンパクトなUSB給電タイトPLL

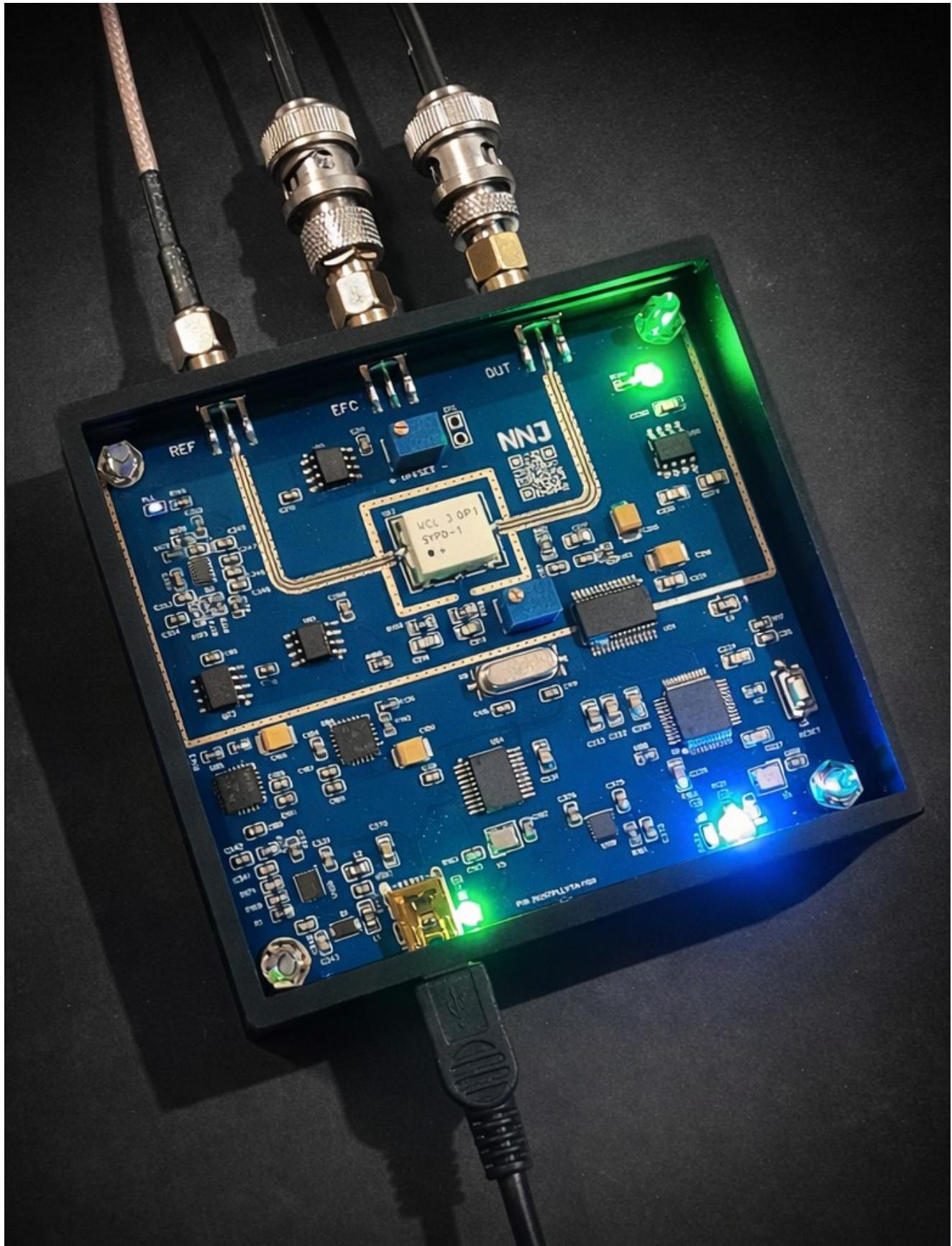

本機は「楽しみのためのプロダクト」として始まった取り組みであり、個人的な設計が約2年をかけて成熟し、量産に耐える完成度の計測器へと発展したものである。高安定度周波数源への深い関心と、それらを正確に特性評価する難しさから生まれた本プロジェクトは、当初から大量生産を目的としていなかった。代わりに、精密計測を愛する熱心な愛好家、研究者、専門家のために、少量ロットのみを製造することにした。本機は、古典的なタイト位相ロックループ (Tight Phase Lock Loop: TPPLL) 技法の実装に最適化されており、OCXO (恒温槽付水晶発振器) をはじめ、ルビジウム標準やそれ以上の標準器に至るまで、高性能発振器の安定度パラメータを詳細に測定できる。24ビットADCにより、アラン偏差、位相雑音、エージング (経時変化) 率、ウォームアップ特性、短期周波数ゆらぎ等の指標に対して非常に高い分解能を提供する。John Miles (KE5FX) のTimeLabとの連携も容易であり、TPPLLの出力をそのまま入力として利用できる。システムの中核は、コンパクトな4層プリント基板に集約されている。位相検出器として高性能ダブルバランス・ミキサ (Mini Circuits SYPD 1+) を採用し、デュアルオペアンプ (加えてEFC出力用のバッファ) による精密アナログ信号コンディショニング、24ビット ADC (ADS1256)、およびデジタル処理と出力のためのSTM32F103マイコンを統合している。外部インターフェースとして、基準 (REF) および被測定 (DUT) 信号用のSMA 50 MHz/Vのスケーリング規約を採用し、周波数誤差をHz単位で直接出力する。RFフロントエンドのレイアウトにおける重要な点は、REFおよびDUT入力からSYPD 1+ミキサへ至る経路に、グラウンド付きコプレーナ導波路 (Grounded Coplanar Waveguide: GCPW) を一貫して用いたことである。GCPWは、動作範囲全体で低反射・良好な信号品質を維持しつつ、精密な50 Ω特性インピーダンスを実現するために選定した。対象周波数 (1 MHz ~ 100 MHz) は必ずしも高度な伝送線路設計を要求しない (通常のマイクロストリップでも十分) ものの、4層の小型設計においてGCPWは、グラウンドビアによるシールド性の向上、隣接配線間のクロストーク低減、基板公差への感度低下、外来干渉に対する耐性向上などの利点をもたらす。これにより位相検出器へクリーンで歪みの少ない信号が供給され、低ノイズフロアと高い測定忠実度に直結する。入力は正弦波と矩形波の双方に対応し、相互に混合することも可能である (ただし正弦波と矩形波の比較では位相雑音が高くなる点に注意)。設計思想は、単純性・再現性・精度を重視する。位相検出電圧を慎重に整形し、ユニティ (1倍) スケーリングを適用することで、出力される周波数偏差値は「電圧 (V) と数値的に同一」となり、温度依存のゲイン定数や頻繁な再校正を通常運用で不要にする。本機は精密周波数基準の事実上の標準である10 MHzに対して完全に校正・最適化されているが、約1 MHz ~ 100 MHzの広い範囲でも、非標準周波数でのミキサオフセットに対する小さな補正をユーザが行うことで利用できる。本資料では、理論的背景、詳細なハードウェア構成、アナログ / デジタル信号経路、ファームウェア機能、測定性能、実用例、入手性について技術的に詳述する。

## 背景：タイト位相ロックループ (TPLL) 技法

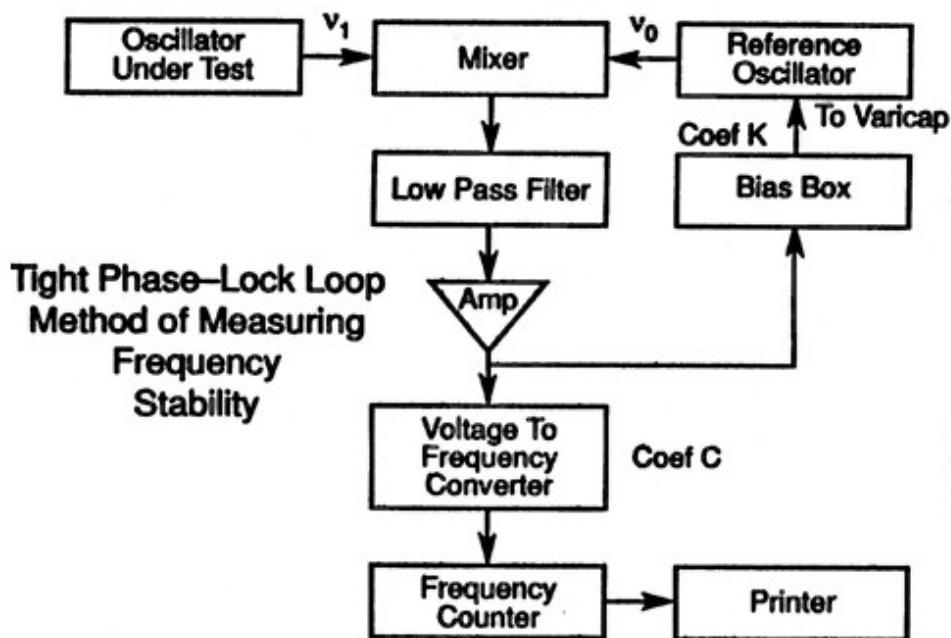

超高安定度の周波数源を評価する際、単純な周波数カウントではなく位相比較技法が長年用いられてきた。主因は、カウンティング法が測定ゲート時間とカウンタ分解能により根本的に制限される一方、位相比較法は2つの発振器間の時間領域挙動を直接捉えることで、はるかに高い感度を得られるためである。その中でもタイト位相ロックループ (TPLL) 法は、簡潔さと達成可能な分解能の点で際立っている。本手法では、意図的に高いループゲインと帯域幅をもつループで2つの発振器を位相同期させる。一方は安定な基準 (REF)、もう一方は被測定 (DUT) である。位相整合を維持するために必要な制御電圧は、REFに対するDUTの瞬時周波数偏差を大きく増幅した表現となる。ループ帯域が関心のあるフリーワーク周波数より十分に広い（すなわちループ応答時間が、解析する平均化時間より十分短い）場合、誤差信号は位相ゆらぎの表現から周波数ゆらぎの表現へと移行する。この積分効果が鍵であり、DUTの短期ノイズや不安定性は制御電圧へ完全に転写される一方、REFの寄与はフィードバックにより抑圧される。長期ドリフトは適切なバイアスおよびフィルタで分離できる。

本技法は数十年にわたり周波数計測の中核であり、NIST（米国標準技術研究所）のTime and Frequency Divisionは、信号源評価のハンドブックで明確かつ権威ある説明を提示している。

Figure 1.7

### D. タイト位相ロックループ法

第2のPLL法はルーズPLLと本質的に同じであるが、本ケースではループがタイト位相ロック状態、すなわちループ応答時間が関心のあるサンプル時間よりはるかに短い（典型的に数ミリ秒）状態にある。こうした場合、位相ゆらぎが積分されるため、電圧出力は2つの発振器間の周波数ゆらぎに比例し、（ループ応答時間より長いサンプル時間に対しては）位相ゆらぎには比例しなくなる。バイアスピロックスはバリキャップへの電圧を、十分に線形で適切な値の同調点に調整するために用いられる。バイアスピロックス手前の（ゼロからわずかにオフセットされた）電圧ゆらぎは電圧 周波数変換器に入力され、さらに周波数カウンタへ供給される。そこで、この発振器ペア間の不安定性が大きく増幅された周波数ゆらぎとして読み出される。周波数カウンタのデータはロガーで記録される。バリキャップ係数と電圧 周波数変換器係数から、発振器間の分数周波数変動  $y_i$  ( $i$  は  $i$  番目の測定) を求める。周波数カウンタの分解能  $1 \text{ Hz}$  に対し  $10^{-1}$  の感度を達成することは難しくなく、本システムは優れた精密度を提供する。

NIST法の初期実装は主にアナログで、チャートレコーダ、電圧 周波数変換器、機械式バイアス調整に依存していた。その後、John Miles (KE5FX) と TimeLabなどのソフトウェアツールにより、デジタルデータ取得と自動後処理が導入され、近代化が進んだ。本機は、この系譜をさらに発展させたものである。従来の電圧 周波数変換器 + カウンタのチェーンを、24ビットADCによる直接デジタル化とマイコンでのスケーリングへ置き換えることで、複数の変換誤差やドリフト源を排除した。意図的な  $1 \text{ Hz/V}$  スケーリングは典型的なOCXOのEFC感度と自然に整合し、シリアル出力は、バリキャップ係数や中間変換器の校正をセットアップ毎に行うことなく、瞬時の周波数偏差 (Hz) を直接提供する。こ

の直接読み出しにより、リアルタイム監視と、後段のアラン偏差解析に向けた長期ロギングが大幅に簡素化される。

## システム概要

TPLL V1/Aは約  $7 \times 8$  cm のコンパクトな4層PCBに実装され、ベンチトップ用途にも組み込み用途にも適する。主な外部インターフェースは以下のとおり。

・REF ( 基準発振器 )

・DUT ( 被測定発振器 )

・バッファ付きEFC出力用SMAコネクタ × 2

・低インピーダンスでフィルタされた誤差電圧を供給し、発振器の制御端子へ直接接続できる

・UART出力 ( 115200 baud, 8N1 )

・整形済みデータをストリーミング

・複数のLED：測定アクティビティ ( ハートビート )、PLL基本ロック状態、タイト位相ロック状態 (  $\pm 5000.0$   $\mu$ Vレンジでトグル )

・データ出力、デジタル / アナログ電源レール状態の表示

・USB Type Mini B：典型消費電流 100 mA 未満

信号チェーンは単純だが高度に最適化されている。

REFおよびDUT信号をMini Circuits SYPD 1+ダブルバランス・ミキサのLOおよびRFポートへ入力し、位相差に比例する直流成分を多く含むIF出力を得る。

IF信号を多段の受動RCローパスで処理し、RF漏れや高次生成物を除去する。精密デュアルオペアンプでフィルタ後信号を処理し、1段目で誤差電圧に制御ゲインを与え、2段目で低インピーダンスのバッファとしてEFC出力コネクタおよびADS1256の差動入力ペアへ供給する。並列の監視経路として、増幅前のミキサ出力をADS1256の第2差動入力ペアへ導き、未増幅と増幅済み誤差信号を同時にデジタイズできる。STM32F103はADCデータを取得し、平均化とオフセット補正を実施し、主チャネルに1 Hz/Vスケーリングを適用して、周波数誤差 ( Hz ) と診断用EFC電圧 (  $\mu$ V ) を連続的に出力する。この2チャネル測定アプローチにより、増幅チャネルは高感度の主読出しを提供し、未増幅チャネルはミキサ挙動の把握や診断・トラブルシュートに有用な情報を与える。

## 動作モード

本システムは、計測およびディシプリニング用途に応じて2つの動作モードを備える。

モードA（古典的・対称構成 / 安定度評価用）同等性能の2台の発振器（例：同型OCXOや周波数基準）を直接比較する。REF入力に一方、DUT入力にもう一方を接続し、EFC出力をREF側の制御端子へ接続する。これにより、タイトPLL測定が成立し、ロギングされた周波数誤差は2台の相対不安定性を反映する。アラン偏差の算出や、個別発振器の寄与分離に適する。

モードB（非対称構成 / ディシプリニング用）低安定度の発振器（OCXO/TCXOなど）を、高精度基準（ルビジウム標準、セシウム、GPSDOなど）へロックする。重要点として、モードAとは入力割り当てが逆である。高精度源をDUT入力へ、ディシプリンされる発振器（制御される側）をREF入力へ接続し、そのEFC端子を本機の出力で駆動する。この反転によりループ極性が正しくなり、誤差電圧がREF発振器を優れたDUT基準へ整合させる方向に作用する。本モードでは、高精度源の短・中期安定度がディシプリン側へ実質的に転写され、GPSや原子標準の長期精度も活用できる。ストリーミングされる周波数誤差データは両モードで有効である。

## ハードウェア設計

RFフロントエンドとアナログ信号コンディショニング RF部の中心はMini Circuits

SYPD 1+ダブルバランス・ミキサであり、広帯域 (1~100

MHz仕様)、高いアイソレーション、低い変換損失を理由に選定した。ミキサのIFポート直後には、二段直列のRCローパスフィルタを配置し、残留RF漏れ、和周波成分、高周波ノイズを強力に減衰させる。カットオフ周波数は、ループ帯域を確保しつつ、群遅延と直流安定性を両立するよう選定している。アナログ部の核はAnalog DevicesのADA4898ファミリのオペアンプである。精密・高ダイナミックレンジ用途に適した特性(超低電圧雑音:典型0.9 nV/Hz、低歪、高スルーレート:55 V/μs、μV級オフセット、pA級バイアス電流)により、系のノイズフロアへの寄与を極小化し、微小な位相検出信号を忠実かつ線形に増幅できる。信号フローは以下の通りである。・二段RCフィルタ後のミキサ出力を、ADA4898 2(デュアル)の第1チャネルへ入力し、非反転増幅器として構成する。ゲインは精密ポテンショメータによりユーザ調整でき、通常の位相変動を適切なフルスケールへ割り当てつつ、線形性維持と飽和回避を行う。・増幅出力は並列に分岐し、(1)同じADA4898 2の第2チャネル(ユニティゲイン・バッファ)へ入り、追加の受動RCフィルタ(ループ安定性とノイズ低減)を経て、ADS1256の差動入力ペアへ供給される。(2)別のADA4898 1(シングル)をユニティゲイン・バッファとして用い、外部EFC出力コネクタを低インピーダンスで駆動する。この構成により、高ゲインで整形された誤差信号を高分解能でデジタル捕捉できると同時に、クリーンで低インピーダンスなアナログEFC電圧をループ閉鎖用に提供できる。さらに、ミキサ出力からの未増幅経路も並列に第2差動ADCペアへ入力され、診断モニタとして利用できる。

Texas Instruments製ADS1256(24ビットADC)は、2つのチャネルペアをいずれも完全差動で動作させ、精密2.5 V外部リファレンスを用いる。1000

SPS動作(内部平均化併用)により、非常に優れたノイズ性能を得る。電源とグラウンドィング設計目標とするμV級ノイズフロアを達成する上で、特にUSB給電という条件下では、電源の健全性が重要課題となる。本基板は4つのLDOを用いて機能ブロックごとにレールを分離し、総消費電力が小さいにもかかわらずクロストークを最小化し、極めてクリーンな電源を実現している。USBの5 V入力は一次フィルタを経て、以下へ分配される。

- STM32F103および周辺ロジック用のデジタルLDO

- ADS1256のデジタルIFおよびリファレンス回路用の個別LDO・アナログ機能用の正電源LDO 最も重要なレイアウト集約的なのはアナログフロントエンドの電源であり、デュアルオペアンプとフィルタ回路には真の両電源が必要である。これをTexas InstrumentsのLM27762(チャージポンプ方式のデュアル出力レギュレータ)で実現し、単一正電源から低ノイズの+5 V/-5 Vレールを生成する。LM27762の配線・給電・レイアウト最適化はPCB設計上の最大難所の一つであった。フライングコンデンサの配置、専用の電源/グラウンド島、広範なローカルデカップリングを適切に行うため、複数回の試作(および個別のレイアウトブロック検討)を要した。さらに、4層スタックアップ上でアナログGNDとデジタルGNDを意図的に分離し、電源入口近傍の一点(スター接続)でのみ接続している。これはデジタルスイッチング電流のアナログ汚染を防ぐ古典的混載信号手法であるが、意図しないグラウンドループやスロットアンテナを生まないよう、部品配置と配線には極度の注意が必要であり、ミキサ部からのRF漏れを拾わない設計配慮を要する。

## デジタル部とファームウェア実装

デジタル部とファームウェア実装 デジタルコアはSTM32F103C8T6であり、性能と周辺機能のバランス、開発ツールの充実を理由に選定した。ファームウェアはC言語（STM32標準ペリフェラルライブラリ）で実装し、意図的に最小かつ決定論的に保っている。OSは用いず、割り込み多用の構成も避け、測定ループの低ジッタと予測可能なタイミングを確保する。

電源投入後、システムクロック、GPIO、UART（115200 baud、0.1 s出力レート）、SPI経由でのADS1256初期化を行い、その後無限ループで2つの差動ADCチャネルを1000 SPSで連続取得する。各測定サイクルでは、各チャネルについて連続8サンプルを加算平均し、ノイズを大きく低減することで有効更新レートは約10 Hzとなる。ADCコードは2.5 Vリファレンスを用いた双極性差動の式で電圧へ換算する。設計周波数10 MHzにおけるSYPD 1+のデータシート仕様に基づき、主（增幅）チャネルには小さな固定DCオフセット補正を加え、残留ミキサ不平衡をヌルする。増幅チャネルの電圧は1 Hz/V規約により、そのまま周波数誤差（Hz）として解釈される。UARTには以下のような整形行を連続出力し、GPIO駆動のLEDにより視覚的フィードバックを提供する（例：列1は周波数、列2はミキサ出力電圧の読み）。

```

1.790728e+00 -3359.046173

1.783133e+00 -3453.221512

1.791057e+00 -3301.825714

1.791064e+00 -3484.215927

1.777067e+00 -3485.408020

1.776427e+00 -3561.105919

1.776253e+00 -3513.422203

1.770705e+00 -3637.399864

1.763964e+00 -3694.620323

```

この簡潔な実装により、堅牢で再現性の高い性能を確保しつつ、容易に改変できる。

## 試験と性能

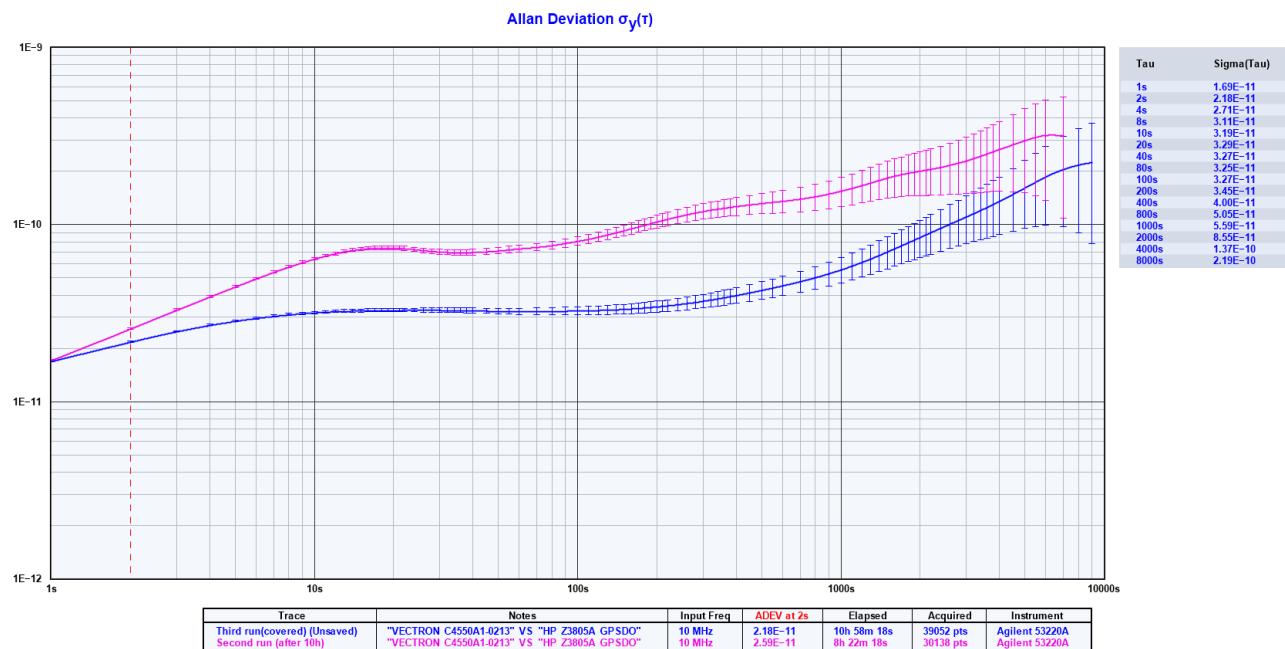

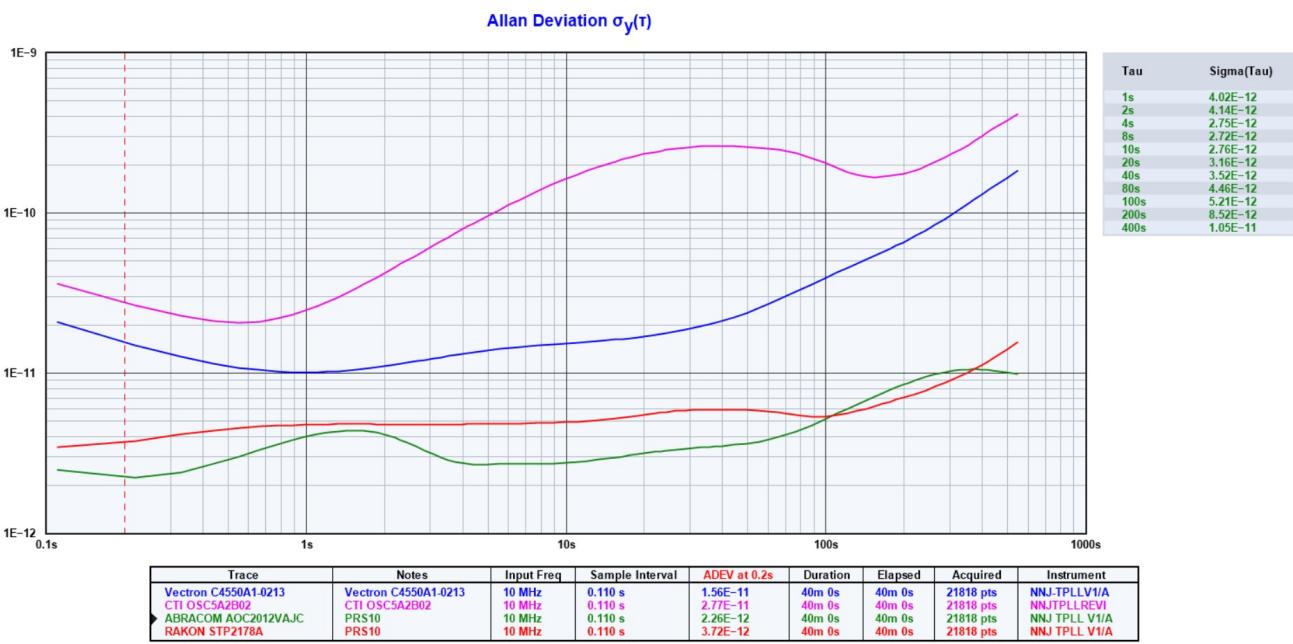

試験と性能 10 MHzにおけるベンチ試験により、サブHz分解能が確認され、系のノイズフロアは「古典的」なタイムインターバルカウンタや同等の業務用システムと比較して整合する分数周波数測定を支える。以下は、Vectron C4550A1 0213を2台用い、合計8時間にわたり実施した試験の一部である。本システムは短～中期安定度解析で最大の効率を発揮するが、数時間規模の取得であっても、従来のタイムインターバルカウンタでは必ずしも得にくい重要な特徴を観測できる。

たとえば、発振器の真の短期安定度 ( $\tau = 1\text{ s} \sim 10\text{ s}$ ) や実際の長期ドリフトを観測できる。技術的に興味深い多くのデバイスでは、短期安定度がタイムインターバルカウンタで直接測定できないことがある。注：本測定は、同一OCXO 2台を専用ボードに搭載し、安定化電源で給電し、適切な金属筐体に収め、測定開始前に48時間以上通電して熱平衡に到達させた状態で実施した。

これは、Agilent 53220A と GPSDO (<https://ampnnts.ru>) を用いた直接比較である。

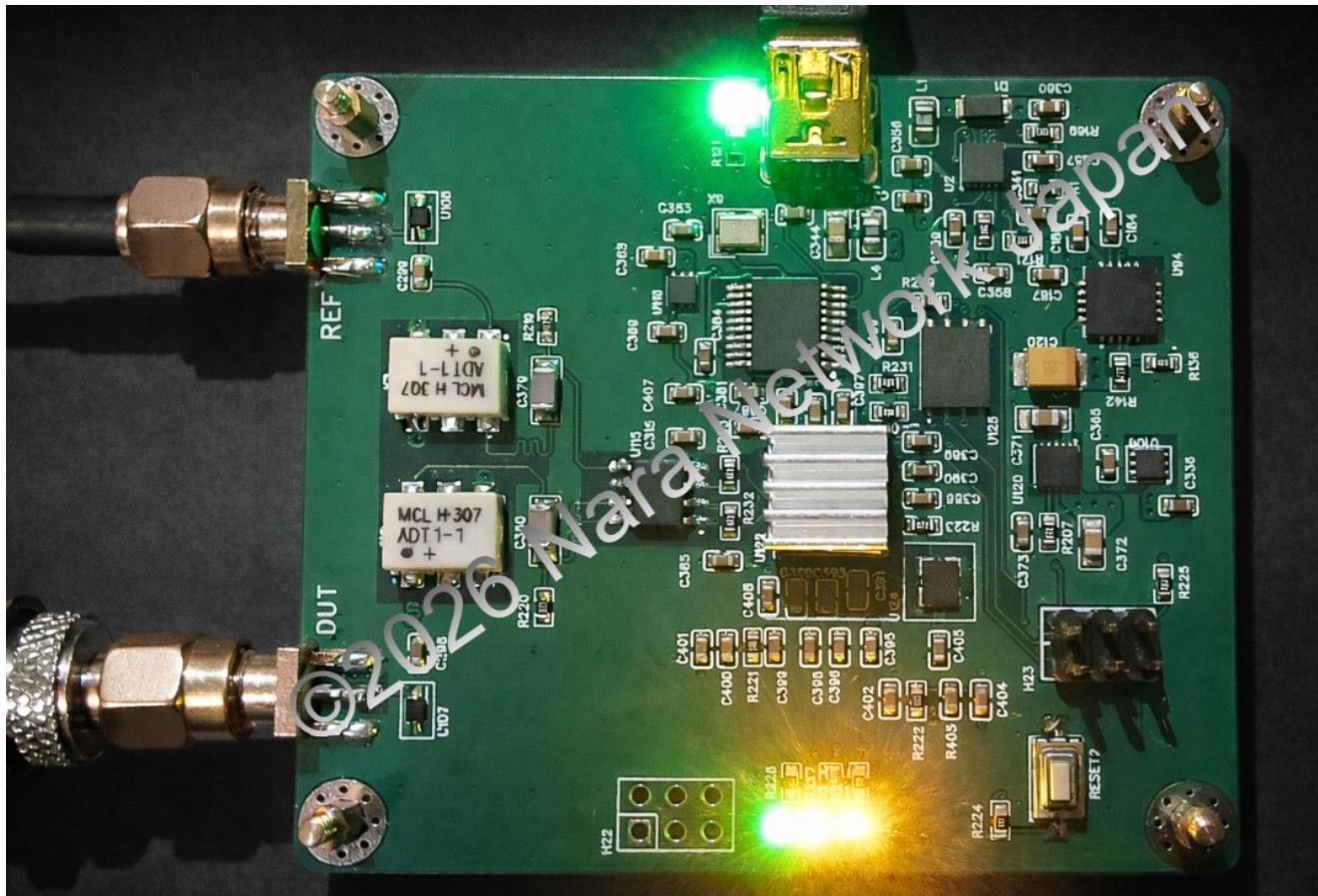

ampnntsのレポートで用いられた正確な試験条件は不明である。しかし、相関が観測されたにもかかわらず、私は独自に開発したFPGAベースの測定システムにより独立検証を実施した（詳細は将来別途報告予定）。本システムは、100 MHzの粗カウンタと、iCE40HX8K FPGA上のキャリーチェーン型タップ遅延線（TDL）を組み合わせたタイムインターバルカウンタを実装し、微小時間分解能を得る。

ここに、開発中プロトタイプ（REV

A) の写真を示す。本プロトタイプは将来的に提供可能となるかもしれない。測定は、TPLLV1/Aで試験したのと同じOCXOに対して、独立の基準源としてPRS10ルビジウム周波数標準を用いて実施した。REFおよびDUTのエッジを独立にタイムスタンプし、その相対時間差を周期的に計算・報告して、位相および周波数安定度解析に供する。

異なる基準標準と完全に独立したハードウェアプラットフォームを用いながら、

sで優れた一致が得られたことは、本測定系の妥当性を強く裏付けるものである。 > 10

以下の測定は、入手可能な複数の発振器を用いて実施した。あるデバイスは同一OCXOをDUTとREFに用いる「純粋」TPLL構成で評価し、別のケースではPRS10ルビジウム周波数標準を基準として使用した。後者の場合、ルビジウム基準に対して安定度の劣る源を比較する際の標準的手順として、DUTに小さく精密に制御された周波数（電圧）補償を与え、ルビジウム基準に整合させて適切な位相ロックと意味のある位相差測定を成立させた。

Abracon発振器は未使用の新品であり、これらの測定のために専用テストボードへ搭載した。

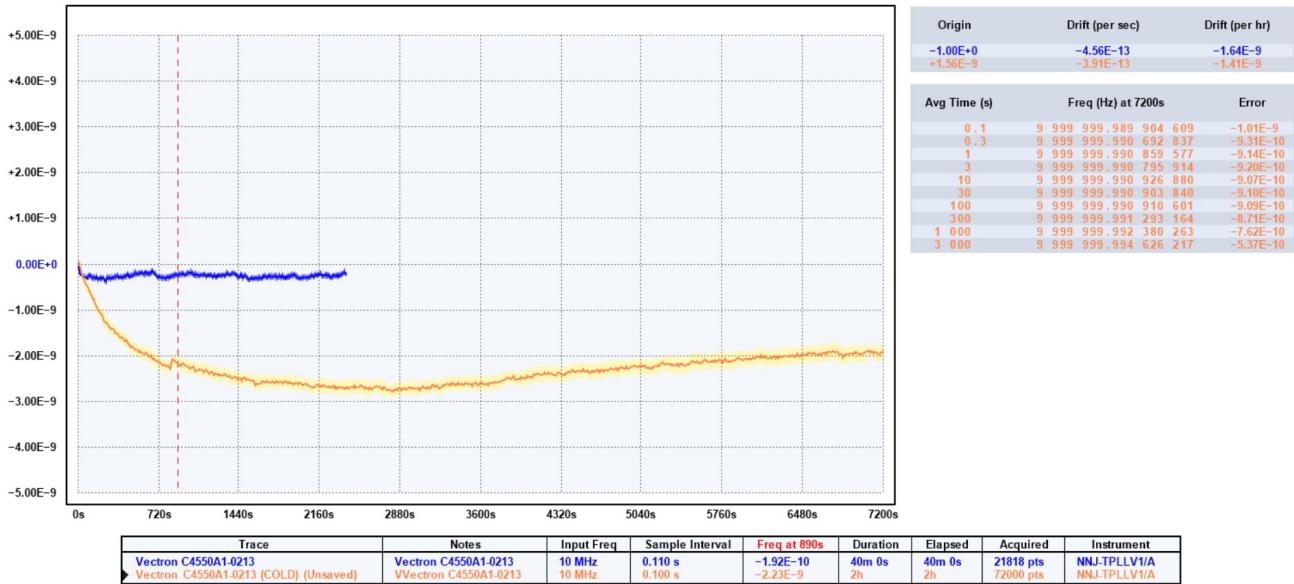

## 発振器ドリフトおよびウォームアップ特性

発振器ドリフトおよびウォームアップ特性 TPLL V1/A の最も実用的で示唆に富む用途の一つは、発振器の短～中期周波数ドリフト（適切な条件では長期も）とウォームアップ挙動を、追加機材や複雑なセットアップ無しに容易に捕捉できる点である。デバイスからストリーミングされる周波数誤差データを長時間（数時間～数日）にわたりロギングするだけで、高精度なドリフト曲線を生成できる。同一OCXOについて2条件で測定した周波数差（線形残差、ゼロ基準）の例を添付プロットに示す。橙色トレースはコールドスタート直後で、最初の約2000秒にわたり約  $3 \sim 4 \times 10^{-11}$  の明確なリトレースドリフトを示し、その後オープンと水晶が熱平衡へ向かうにつれて安定なプラトーへ収束する。対して青色トレースは同一ユニットを48時間連続運転した後に取得したもので、 $\pm 5 \times 10^{-11}$  以内でほぼゼロ近傍に平坦となり、十分なウォームアップ後に安定度が劇的に改善することを示している。この比較は、ウォームアップ効果の大きさのみならず、 $10^{-11}$  未満の分解能で遅いドリフトを追跡できる本システムの能力を強調する。これによりリトレース誤差、エージング率、環境感度などを定量化しやすくなる。デバイス自身のシリアル出力のみで測定できるという容易さは、高精度計測をより身近なものとし、従来は高価で高度な試験機材を要した微妙な挙動の可視化を可能にする。

Frequency Difference (Linear residual, zero-based)

Averaging window: Per-pixel

## 動作モードと基準コンディショニングの影響

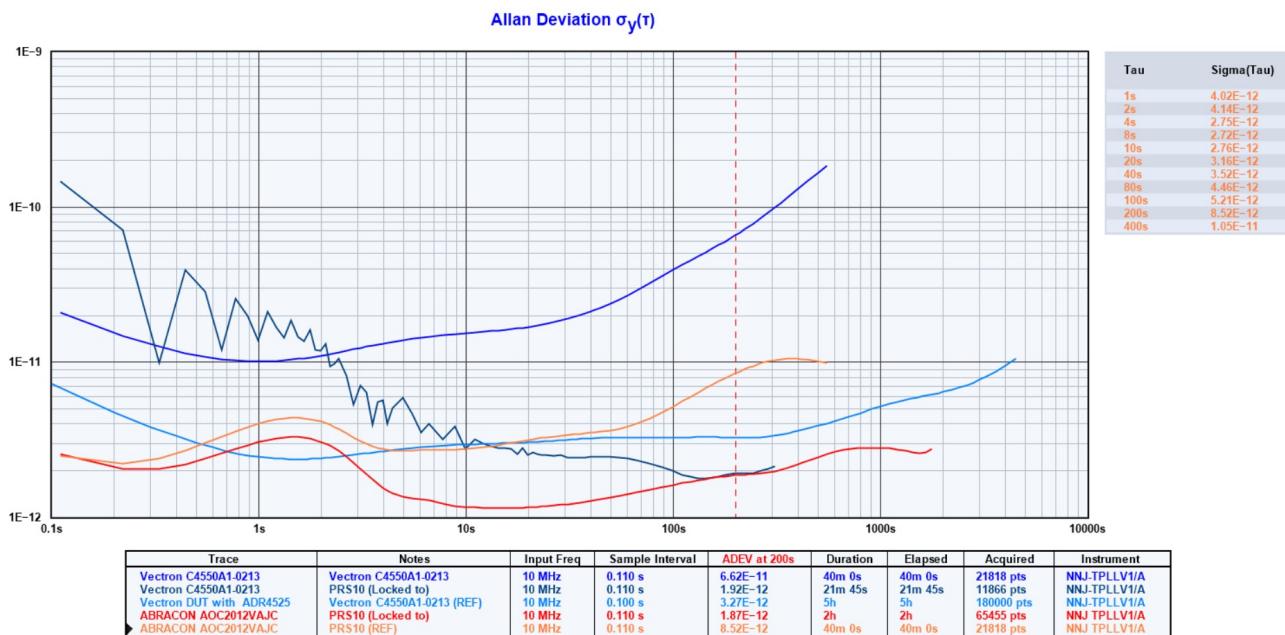

動作モードと基準コンディショニングの影響 本図は、TPLL V1/Aを用いて3つの異なる動作条件で得られたアラン偏差の比較解析を示し、システムの柔軟性と固有の性能限界を示している。

青色トレース（リスト上で上から順にTrace N.1）は、本資料で既に述べたベースライン測定に対応する。この構成では、TPLL V1/Aは標準モードで動作し、同一のVectron C4550A1 0213 OCXO 2台を対称な「純粹」TPLL構成で比較している。したがって本トレースは、REFとDUTが近い性能を持つ場合に達成される固有の短～中期安定度を表す。

Trace N.2はモードBで取得したもので、Vectron OCXOを外部PRS10リビジュウム周波数標準へ位相ロックしている。この場合、アラン偏差は点ごとの変動がより顕著となり、見かけ上より不規則なプロファイルとなる。この挙動はTPLL V1/Aの性能劣化を示すものではなく、OCXOの制御ループダイナミクスと、リビジュウム基準の大幅に高い長期安定度との相互作用を反映している。安定度の劣る発振器を、はるかに安定な源へタイトにディシプリンすると、残留位相誤差系列は制御動作、量子化効果、ループ帯域制限に支配され、短いでADEVの局所分散増大として現れる。Trace N.3はベースライン構成の変形で、DUTの周波数制御入力（EFC）を外部精密電圧リファレンス（ADR4525）でバイアスした。EFCへ印加する基準電圧を慎重に設定し、制御ノイズ注入を最小化しつつOCXOのフリーラン周波数

を整合させた。ADR4525は高精度・低雑音電圧リファレンスであり、初期精度  $\pm 0.02\%$ 、低温度係数（最小  $2 \text{ ppm/}^{\circ}\text{C}$ ）、低出力雑音（ $0.1 \text{ Hz} \sim 10 \text{ Hz}$ で約  $1 \text{ }\mu\text{V pp}$ ）、優れた長期ドリフト特性を持つ。これらは、電圧雑音とドリフトが直接周波数不安定性へ変換される感度の高いOCXO制御入力のバイアスに非常に適している。図が示す通り、ADR4525の使用により、ルビジウムロックの場合と比べて短い

でより滑らかで低いアラン偏差が得られ、OCXO制御電圧のコンディショニングが、発振器の固有ノイズフロア近傍での有効安定度を大きく改善し得ることが確認される。ただし最終的な性能は、OCXO自身の同調感度および物理的限界により制約される点を強調しておく必要がある。TPLL V1/AIは、同一発振器同士、外部原子標準、精密電圧バイアスなど多様な構成で動作できる柔軟で低雑音なプラットフォームを提供するが、達成可能な安定度は、DUTが印加された基準または制御信号へ忠実に追従できる能力に本質的に依存する。ABRACON AOC2012VAJCについて、Trace N.4 (PRS10ヘロック : モードB) が、ルビジウムヘロックしたVectron (Trace N.2) と  $> 100 \text{ s}$  でほぼ完全に一致し、一方でTrace N.5は、ABRACONをルビジウムヘロックしたものをREFとしてフリーランで比較した結果であることが、この確認となる。

## 環境条件への感度

環境条件への感度 上図は、同一のVectron C4550A1 0213 OCXOを用いて得た追加のアラン偏差比較であり、TPLL V1/A測定系が環境・熱条件に対してどの程度敏感であるかを示すことを意図している。Trace 1は、電源投入直後に取得したコールドスタート条件（前述）である。予想通り、アラン偏差は過渡的な熱効果とウォームアップドリフトに支配され、中～長い平均化時間で不安定度が高い。Trace 2は、熱平衡に到達した後、2台のOCXOを開放型エンクロージャ内で動作させて取得した。この条件では短期・長期とも、残留気流や不十分な熱遮蔽の影響が残る。Trace 3は、同一構成でOCXOを完全に閉じた金属筐体内に収めた場合である。この配置は熱的隔離と機械的遮蔽を強化し、広い範囲でアラン偏差の明確な低減をもたらし、3条件中で最も安定かつ再現性の高い結果となる。これらトレースの明確な分離は、24ビットADCに基づく位相／制御測定アーキテクチャと低雑音信号チェーンによって実現されたTPLL V1/Aの高い感度と分解能を示している。従来のPLL測定やカウンタ測定では見えにくい、熱・環境条件の微妙な差異が容易に分解される。以上より、TPLL V1/Aは絶対安定度測定に適するだけでなく、ウォームアップ挙動、筐体の有効性、環境結合の評価に対する強力な診断ツールとしても有用であることが確認される。

## 入手性

入手性 本機は情熱プロジェクトとして生まれた経緯から、Nara Network Japanにより小ロットで限定生産され、当面は当社ウェブサイト（[www.naranetwork.com](http://www.naranetwork.com)）を通じてのみ提供される。各ユニットは札幌の小規模ラボにて個別に組立・試験・校正を行う。品質管理および部材調達のため、納期は最大25日程度を見込んでいただきたい。